Alexander Rogelio Ramírez Zaldívar<sup>1</sup>, Abel Hernández Violat<sup>1</sup>, Yunior Ibarra Guerra<sup>1</sup>

<sup>1</sup>Centro de Investigación y Desarrollo de Electrónica y Mecánica, CID MECATRONICS, Cuba <sup>1</sup>cid3@reduim.cu

### **RESUMEN**

La formación digital del diagrama de radiación constituye una de las tendencias actuales en la fabricación de arreglos de antenas. En el presente trabajo se expone la realización del núcleo de un sistema con escaneo electrónico del haz en un FPGA, a partir del diseño realizado en Simulink (MATLAB) y exportado a VHDL para su síntesis en el dispositivo lógico programable. Con el proyecto se obtiene un método para el desarrollo y puesta a punto de este tipo de procesadores, que puede ser extendido a aplicaciones más complejas en la línea de trabajo, como es el caso de las antenas inteligentes con procesamiento adaptivo de los datos. La principal contribución es la implementación del procesador para un arreglo digital con escaneo electrónico, a partir de la descripción realizada desde MATLAB.

PALABRAS CLAVES: Formación digital del haz, FPGA, Simulink.

## ANTENNA'S SYSTEM PROCESSOR DESIGN WITH DIGITAL BEAMFORMING USING FPGA

### **ABSTRACT**

Digital beamforming constitutes one of the actual tendencies in the construction of the antenna's array. The paper presents the core's realization for an electronic beam scan system in FPGA from the digital design implemented in Simulink (MATLAB), and exported to VHDL for its synthesis in the programmable logic device. The work exposes a method to develop and fine-tunes this kind of processor that can be extended to more complex applications within this job's line like smart antennas with adaptive data processing. The main contribution is the processor's implementation for a digital array with an electronic scan from the description made in MATLAB.

**INDEX TERMS:** Digital beamforming, FPGA, Simulink.

## 1. INTRODUCCIÓN

En términos de antenas, un sistema con formación digital del diagrama o Beamforming (anglicismo), es un arreglo de unidades de radiación, cuya información se digitaliza y envía a un bloque de procesamiento para la conformación con técnicas digitales de una respuesta espacial. El coeficiente de peso aplicado a cada canal determina la característica resultante del arreglo. Una de las primeras aplicaciones de este tipo de procesadores fue el control electrónico de la dirección principal de radiación, ofreciendo una serie de ventajas con respecto a las antenas con exploración mecánica y aquellas donde el escaneo se garantizaba con elementos de radiofrecuencia controlados digitalmente [1-3].

El empleo de Arreglos de Compuertas Programables por Campo (FPGA, por sus siglas en inglés) constituye una solución eficiente para la implementación de dichos sistemas, debido fundamentalmente a su escalabilidad, flexibilidad y posibilidad de evitar inconvenientes frecuentes en los formadores de diagramas analógicos [4]. Con la utilización de FPGA es posible diseñar configuraciones de trabajo variadas, que incluyan la transmisión de datos por red para su procesamiento en dispositivos con mayor capacidad de cómputo [5]. El presente artículo propone la implementación del procesamiento en este tipo de dispositivo, muy útil para aplicaciones en tiempo real.

Lo antes expuesto ha introducido en la implementación de formadores digitales de diagramas de radiación, una línea de diseño basada en el empleo de FPGA. Los trabajos [6-8] muestran proyectos sustentados en dicha tecnología, con aplicaciones que van desde el procesamiento ultrasónico hasta sistemas de radar con formación de imágenes.

La amplia utilización y fortaleza alcanzada por los sistemas digitales, ha implicado un desarrollo paralelo de herramientas que facilitan su diseño y verificación. El software computacional MATLAB es un ejemplo de ello, al incluir la posibilidad de realizar ambas acciones en el ambiente de trabajo del Simulink, permitiendo exportar los bloques obtenidos a Lenguajes de Descripción de Hardware (HDL, por sus siglas en inglés) para su posterior síntesis en los dispositivos programables. Existen ya herramientas optimizadas para el trabajo con familias de dispositivos específicas: en [9] se muestra el desarrollo de un Beamforming transmisor empleando Xilinx System Generator for DSP. Con el proyecto actual se realiza un diseño en Simulink sin el empleo de herramientas predefinidas, posibilitando mayor versatilidad en su destino final.

El objetivo del trabajo es emplear este método, para la obtención del procesador de un sistema con formación digital del diagrama, y su verificación funcional en FPGA. Como aporte fundamental se obtiene la implementación en FPGA del procesador de un sistema con escaneo electrónico, a partir de una descripción realizada de forma íntegra con MATLAB.

## 2. MATERIALES Y MÉTODOS

En la presente sección se realizará un breve desarrollo de los conceptos y elementos básicos necesarios, para facilitar la comprensión del proyecto. Incluye aspectos relacionados a la teoría de formación del diagrama de radiación en arreglos de antenas, el desarrollo de sistemas digitales utilizando arreglos de compuertas lógicas y la utilización del MATLAB para la creación de códigos HDL sintetizables.

## Formación del haz convencional

Para un arreglo de N antenas ubicadas aleatoriamente sobre el cual incide un frente de onda plano procedente de la dirección ( $\theta_k$ ,  $\Phi_k$ ), la diferencia entre las señales recibidas por sus elementos quedará determinada únicamente por la variación del retardo sufrido por la onda, para llegar a cada unidad de radiación que lo forma [3].

Al introducir en los diferentes canales un factor complejo para compensar la diferencia de recorrido de la onda con respecto al origen de coordenadas, y posteriormente efectuar la suma de los datos resultantes del proceso, se obtendrá como salida final la señal original incidente sobre el sistema [10].

En la formación convencional del haz se sigue un principio similar al explicado previamente: la información recibida por cada elemento es multiplicada por un coeficiente de peso  $(W_n)$ , cuya fase garantiza la recepción de las señales en determinada dirección. Su valor depende de la frecuencia central de trabajo y el retardo a compensar, este último a su vez, está determinado por la disposición geométrica de las antenas, así como la dirección deseada [11]. La ecuación (1) muestra la expresión empleada para el cálculo del peso asociado a un canal.

$$W_n = e^{j2\pi f_0 \tau_n} \tag{1}$$

donde:

$f_0$ : Frecuencia central de trabajo

$\tau_n$ : Retardo correspondiente al enésimo elemento

## Formación digital del haz sobre FPGA

Los sistemas con formación digital del diagrama (DBF, del inglés Digital Beamfomer) realizan la digitalización de la información procedente de cada canal y posteriormente efectúan la multiplicación por el factor de peso [12]. Un DBF está compuesto por tres secciones fundamentales: arreglo de radiadores, sistema de recepción digital y procesador de las señales. Este último, centro del presente trabajo, se encarga de determinar el valor de los coeficientes y ejecutar el producto complejo con las señales correspondientes [13].

La implementación realizada se llevará a cabo sobre FPGA dado por las facilidades que presentan con relación a otros dispositivos lógicos programables [14] y la posibilidad de incorporar el proceso de recepción digital de las señales mediante tarjetas de conversión [15]. Para su verificación funcional se utilizará la tarjeta DE0-Nano mostrada en la Fig. 1, por su disponibilidad y facilidad de manejo [16]. Un desarrollo utilizable del diseño propuesto debe ser realizado en un FPGA con posibilidades de incorporación de tarjetas de conversión para la digitalización de las señales de cada canal.

ISSN 1729-3804

Figura 1: Dispositivo de hardware empleado.

El diseño digital del sistema será realizado con el empleo de la plataforma de simulación multidominio Simulink (propia del MATLAB). Esta presenta un conjunto de librerías con posibilidad de exportación a VHDL sintetizable [17], accesibles desde la ventana de comandos mediante la sentencia *hdllib*.

## 3. IMPLEMENTACIÓN DEL PROCESADOR DEL SISTEMA

A partir de lo visto en la parte inicial del trabajo, el proceso de diseño puede ser dividido en tres etapas fundamentales:

- a. Obtención del valor de los pesos para cada canal de recepción en función de las características del sistema para el cual será empleado (frecuencia de trabajo y configuración geométrica).

- b. Diseño del sistema digital en Simulink y exportación a VHDL.

- c. Implementación del sistema sobre hardware programable.

Como parte de la primera etapa se selecciona la realización del procesador para un arreglo de antenas lineal, operando a una frecuencia de 1.5 GHz y formado por 10 elementos de radiación distribuidos uniformemente a lo largo del eje y con una separación de media longitud de onda de trabajo.

En función de los datos anteriores, la expresión (1) queda redefinida como se muestra a continuación:

$$W_n = e^{j\frac{2\pi}{\lambda}py_nsen(\theta_k)} \tag{2}$$

donde:

$py_n$ : Posición del elemento

El diseño en Simulink cuenta con tres secciones fundamentales:

- a. Cálculo de los pesos en función del ángulo de radiación deseado.

- b. Aplicación de los pesos en cada canal.

- c. Obtención de la señal de salida.

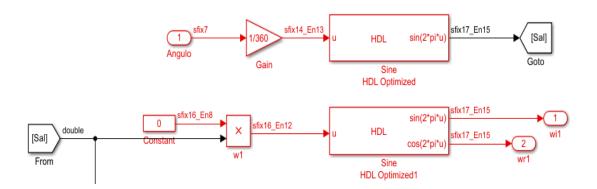

Para el cálculo de los pesos se tiene el esquema mostrado en la Fig. 2. La dirección de radiación deseada se introduce con un formato de 7 bits con signo, lo cual garantiza el establecimiento de ángulos que van desde -60° hasta 60°. La función seno es calculada con el empleo del bloque optimizado para HDL *Sine*, previamente el valor del ángulo es acondicionado en el bloque *Gain* donde es realizada su conversión a radianes y una variación adicional

necesaria por las propias características del bloque *Sine*. Esta etapa es común para todos los canales y se corresponde con el cálculo de  $sen(\theta_k)$  en la ecuación (2).

Figura 2: Esquema en Simulink para el cálculo de los coeficientes de peso.

La salida del proceso anterior es multiplicada por la constante *Constant*, cuyo valor varía de un elemento a otro y su amplitud se determina por el factor  $\frac{2\pi}{\lambda}py_n$  y modificaciones requeridas por los bloques que le siguen al procesamiento. Finalmente es necesario obtener las componentes real e imaginaria del peso, para ello se emplea el bloque *Sine* configurado para brindar a su salida tanto el seno como el coseno del valor a su entrada, garantizando su descomposición IQ.

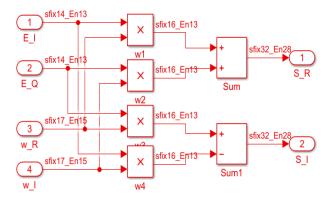

La aplicación de los pesos a las señales correspondientes es realizada mediante el esquema mostrado en la Fig. 3. Como se aprecia recibe a su entrada las componentes en fase y cuadratura de la señal del canal correspondiente (E\_I y E\_Q), así como el peso determinado a partir de la dirección de radiación requerida. En su interior se efectúa la multiplicación compleja de ambas señales. A la salida se obtienen las componentes de la señal de entrada al canal modificadas por el coeficiente de peso complejo.

Figura 3: Esquema en Simulink para la aplicación de los pesos.

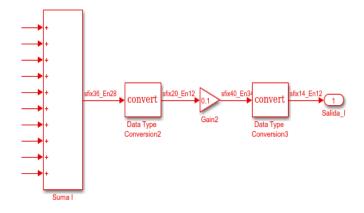

El último paso requiere la combinación lineal de los datos procedentes de los diferentes elementos del arreglo de antenas. Para ello se emplea el esquema mostrado en la Fig. 4 compuesto por un bloque sumador de 10 canales cuya salida es normalizada con respecto al total de elementos. Nótese la existencia de bloques intermedios para la conversión de datos. El primero, se emplea para limitar la longitud del bus resultante del proceso de la suma y garantizar así que el resultado de la normalización posterior no exceda el ancho de bus permisible en la implementación hardware. El segundo, permite adecuar la salida total del procesador a los parámetros de la implementación del sistema. Este bloque se implementa por separado para los canales en fase y cuadratura.

Durante la etapa de diseño en Simulink es necesario controlar el crecimiento de los datos con la realización de operaciones matemáticas con el objetivo de evitar la saturación del sistema durante su implementación. En este proceso juegan un papel fundamental los bloques de conversión mencionados con anterioridad.

ISSN 1729-3804

Figura 4: Esquema en Simulink para la obtención de la señal de salida.

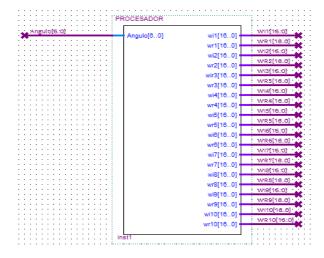

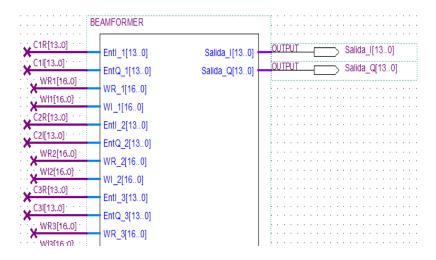

Una vez elaborado y verificado el sistema digital en Simulink, es exportado a HDL para la descripción del procesador en el FPGA. Para ello, se divide el diseño realizado en dos secciones: una primera asociada al cálculo de los coeficientes de peso necesarios en función del ángulo de dirección y otra que incluye el producto complejo de dichos pesos por los canales correspondientes y la posterior combinación lineal de cada una de las líneas de recepción. Las figuras (5) y (6) muestran los bloques resultantes en el diagrama esquemático realizado en Quartus II tras el proceso de exportación.

Figura 5: Bloque en Quartus II para el cálculo del vector de pesos complejo.

## 4. ANÁLISIS Y DISCUSIÓN DE LOS RESULTADOS

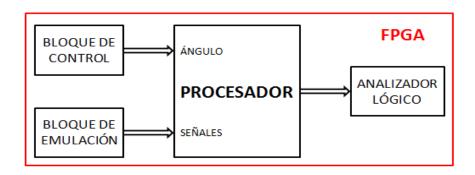

Tras la implementación del procesador para el sistema de antenas con formación del haz digital se verifica su correcto funcionamiento. Para ello fue empleado el esquema mostrado en la Fig. 7.

Durante la validación funcional se utilizó la tarjeta DE0-Nano, la cual no permite la realización de las etapas previas al procesador, pero garantiza la comprobación de su rendimiento. Para emular las señales resultantes del proceso de recepción, se creó un bloque interno en el FPGA, formado por un conjunto de memorias ROM direccionadas por un contador. Los datos almacenados en ellas, contenían la señal recibida por cada canal bajo diferentes condiciones de entrada, las que fueron generadas con el empleo de la herramienta MATLAB, separadas en sus componentes IQ, y

convertidas en valores enteros de 14 bits con signo. La indicación de la dirección de escaneo deseada es realizada por el BLOQUE DE CONTROL, mediante la herramienta In-System Source and Probes Editor, la cual brinda la opción de generar señales internas en el diseño esquemático, cuyo valor puede ser controlado a través de una interfaz gráfica.

Figura 6: Bloque en Quartus II para la aplicación del vector de los pesos.

Figura 7: Esquema de verificación en la tarjeta de desarrollo DE0-Nano.

El conjunto PROCESADOR integra los subsistemas para el cálculo y la aplicación del vector de los pesos desarrollados en Simulink. La representación y análisis de los resultados se realizó empleando el analizador lógico SignalTap II.

Durante las pruebas experimentales se comprobaron tres aspectos fundamentales:

- a. Correcta recepción de las señales.

- b. Escaneo electrónico.

- c. Característica direccional del sistema de antenas.

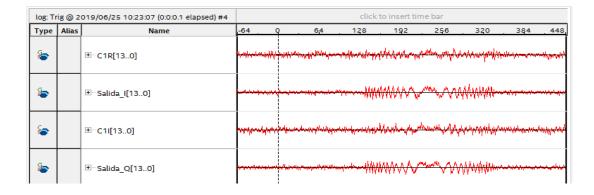

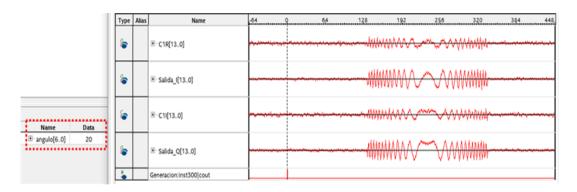

Para el análisis de la correcta recepción de las señales se almacena en el BLOQUE DE EMULACIÓN, la información correspondiente a una onda con modulación lineal de frecuencia recibida desde la dirección normal al arreglo con una SNR=1. Los resultados obtenidos se muestran en la Fig. 8.

En la imagen se representan las componentes reales e imaginarias de la señal recibida por el primer elemento del sistema y la salida del procesador, en ese orden. Observe como el procesador garantiza las exigencias de su diseño, mostrando incluso la mejora de SNR propia de los beamformers convencionales.

La ejecución del escaneo electrónico fue valorada a través del almacenamiento en las memorias de los datos, correspondientes a señales incidentes desde diferentes direcciones angulares y apuntando hacia ellas el diagrama de

ISSN 1729-3804

radiación de las antenas para verificar su correcta adquisición. La Fig. 9 muestra los resultados obtenidos para una señal recibida con una inclinación a partir del eje normal de 20° tras el proceso de escaneo del haz. A la izquierda se representa una sección de la interfaz de control.

Figura 8: Salida del procesador.

Figura 9: Respuesta del sistema con el haz escaneado.

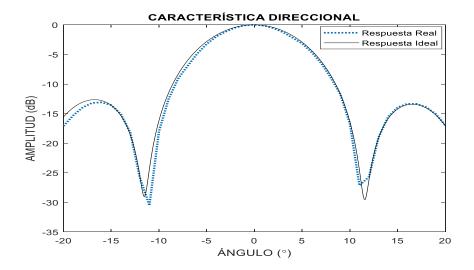

Para la comprobación de la característica direccional del sistema de antenas generada digitalmente, se toma como señal de entrada una interferencia ruidosa (procedente de la dirección normal al arreglo) con una INR elevada. Se varió la dirección principal del procesador en un rango de  $\pm 20^{\circ}$  empleando el BLOQUE DE CONTROL. La señal de salida en cada punto fue extraída del simulador lógico y procesada en MATLAB, donde se calculó la potencia recibida en cada posición. Finalmente, se efectuó la normalización de los valores obtenidos con respecto al máximo valor alcanzado y fueron representados en escala logarítmica. El diagrama resultante se muestra en la Fig. 10 (línea de puntos) junto a la característica direccional teórica de un arreglo de antenas como el implementado (línea continua). Se puede apreciar la existencia de una correspondencia entre ambos diagramas de radiación ratificando el funcionamiento del procesador diseñado.

El procesador propuesto permite la realización del escaneo electrónico en un rango de  $\pm 60^{\circ}$  garantizando la recepción sin distorsión de las ondas de radio. Existen puntos en los cuales puede trabajarse en aras de elevar la calidad del sistema, uno de ellos es su flexibilidad: independientemente de la fácil elaboración una vez implementado, se encuentra atado a la estructura física del sistema de antenas para el cual fue calculado, lo cual constituye una deficiencia. Algunos bloques específicos como el empleado para la aplicación de los pesos, pueden ser reutilizados, pero no el procesador en su totalidad. Realizar esta adecuación implicaría un aumento de los recursos requeridos, pero garantizaría la escalabilidad y flexibilidad del conjunto. Independientemente, con los aspectos verificados durante las pruebas funcionales llevadas a cabo, es posible afirmar que la implementación

realizada del procesador para la formación digital del diagrama del arreglo de antenas, cumple con las características necesarias para ser empleado en un sistema con escaneo electrónico, dando cumplimiento al objetivo trazado.

Figura 10: Diagrama de radiación del sistema.

## 5. CONCLUSIONES

Con el presente proyecto fue obtenida la realización íntegra de la elaboración del procesador, para un sistema con escaneo digital del haz empleando la herramienta computacional MATLAB. Aunque se limitó la implementación al control del diagrama para un arreglo lineal de antenas; debido a la facilidad de diseño ofrecida por la herramienta utilizada, es posible explotar la posibilidad de implementar procesadores para sistemas con estructuras geométricas complejas y que empleen algoritmos adaptativos durante la determinación de los pesos. El principal aporte alcanzado con este trabajo, es la realización íntegra del diseño del procesador empleando MATLAB y la síntesis de la descripción obtenida en un FPGA, creando las bases para desarrollar sistemas de mayor envergadura siguiendo la línea de trabajo propuesta.

## RECONOCIMIENTOS

Los autores desean agradecer al colectivo de trabajo de los grupos de Antenas y Procesamiento de señales por su apoyo en la realización del presente trabajo.

## REFERENCIAS

- [1] R. J. Mailloux, «Phased Array Antenna Handbook», Artech House, Norwood, 2005.

- [2] C. Wagner, A. Stelzer and H. J¨ager, «A phased-array radar transmitter based on 77-GHz cascadable transceivers», Microwave Symposium Digest MTT'09, 2009, pp. 73-76.

- [3] W.-D. Wirth, «Radar Techniques Using Array Antennas», Institution of Engineering and Technology, 2001.

- [4] Rao, D. G., A. P. Deshpande, N. S. Murthy, and A. Vengadarajan, "Digital beam former architecture for sixteen elements planar phased array radar", 2013 The International Conference on Technological Advances in Electrical, Electronics and Computer Engineering (TAEECE), 532–537, Konya, 2013.

- [5] W. Shang, Z. Dou, W. Xue, y Y. Li, «Digital beamforming based on FPGA for phased array radar», en 2017 Progress in Electromagnetics Research Symposium Spring (PIERS), may 2017, pp. 437-440, doi: 10.1109/PIERS.2017.8261779.

- [6] M. A. Hassan, A.-B. M. Youssef, y Y. M. Kadah, «Modular FPGA-based digital ultrasound beamforming», en 2011 1st Middle East Conference on Biomedical Engineering, feb. 2011, pp. 134-137, doi: 10.1109/MECBME.2011.5752083.

- [7] R. Khanna, R. Mehra, y Chandni, «FPGA based implementation of pulsed radar with time delay in digital beamforming using partially serial architecture», en 2017 3rd International Conference on Computational Intelligence Communication Technology (CICT), feb. 2017, pp. 1-6, doi: 10.1109/CIACT.2017.7977344.

- [8] M. Harter y T. Zwick, «An FPGA controlled digital beamforming radar sensor with three-dimensional imaging capability», en 2011 12th International Radar Symposium (IRS), sep. 2011, pp. 441-446.

ISSN 1729-3804

- [9] D. C. Rodríguez, E. García y R. B. Miller, «Diseño e Implementación de un Beamformer Transmisor en una FPGA», 2008.

- [10] F. B. Gross, «Smart Antennas with MATLAB», Mc Graw Hill Education, New York, 2015

- [11] H. L.Van Trees, «Optimum Array Processing Part IV», Wiley-Interscience, New York, 2002

- [12] A. D. Brown, «Electronically Scanned Arrays MATLAB Modeling and Simulation», CRC Press, 2012

- [13] A. El Zooghby, «Smart Antenna Engineering», ARTECH HOUSE, 2005

- [14] P. P. Chu, «HTL Hardware design using VHDL. Coding for Efficiency, Portability, and Scalability, Willey-Interscience», 2006

- [15] THDB-ADA User Guide (2015). Available: www.terasic.com

- [16] DE0-Nano User Manual (2015). Available: www.terasic.com

- [17] Simulink User's guide, MathWorks (2019). Available: www.mathworks.com

#### SOBRE LOS AUTORES

Alexander Rogelio Ramírez Zaldívar, nacido en agosto de 1992, es ingeniero en Telecomunicaciones, graduado del Instituto Técnico Militar José Martí en el año 2015. En el 2016 participó en el V Seminario Internacional de Tecnologías de la Información. Actualmente opta por el título académico de Máster en Sistemas Digitales en la Universidad Tecnológica de la Habana José A. Echeverría.

Abel Hernández Violat, es ingeniero Radioelectrónico, graduado del Instituto Técnico Militar José Martí en el año 1997. Ha cursado dos diplomados: Diseño y modernización de Radares y Programación de hardware y computadoras. Investigador Auxiliar desde el 2017. Actualmente opta por la obtención del grado científico de Doctor en Ciencias Técnicas.

Yunior Ibarra Guerra, nacido en agosto de 1992, es ingeniero en Telecomunicaciones, graduado del Instituto Técnico Militar José Martí en el año 2015. En el 2016 participó en el V Seminario Internacional de Tecnologías de la Información. Actualmente opta por el título académico de Máster en Sistemas Digitales en la Universidad Tecnológica de la Habana José A. Echeverría.

## CONFLICTO DE INTERESES

No existen conflictos de intereses de los autores ni de la institución en relación al contenido del artículo aquí reflejado.

## CONTRIBUCIONES DE LOS AUTORES

- Alexander Rogelio Ramírez Zaldívar participó en la conceptualización, preparación, creación y desarrollo del artículo, realizó el diseño del procesador y organizó las pruebas para su verificación.

- Abel Hernández Violat participó en la revisión crítica de cada una de las versiones del borrador del artículo y aprobación de la versión final a publicar.

- Yunior Ibarra Guerra participó en la revisión crítica de cada una de las versiones del borrador del artículo y aprobación de la versión final a publicar.

Esta revista provee acceso libre inmediato a su contenido bajo el principio de hacer disponible gratuitamente investigación al público. Los contenidos de la revista se distribuyen bajo una licencia Creative Commons Attribution-NonCommercial 4.0 Unported License. Se permite la copia y distribución de sus manuscritos por cualquier medio, siempre que mantenga el reconocimiento de sus autores y no se haga uso comercial de las obras.